P4 SmartNIC stories: Intel

This year there where a lot of interesting SmartNIC announcements, not only from the usual NIC vendors but also from some new kids on the block. What is happening in the previously sleepy NIC space? In this blog I will start with analyzing Intel.

In follow up blogs I will look at other vendors (like Pensando, Mellanox/Nvidia, Broadcom) trying to supply (P4) programmable solutions for those rapidly changing NIC requirements.

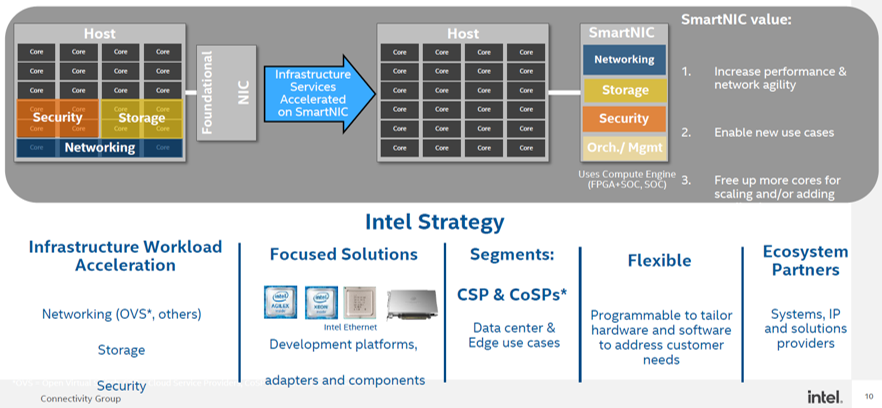

Intel's vision

One of the biggest players in the NIC space is Intel so what do they think about the future of host networking? Hong Hou is the new general manager of Intel’s Connectivity Group and he explained a week ago in a interview for The Next Platform: “For Intel, we want to provide intelligence and programmability in a flexible network that can handle the complexity of the emerging workloads. Our vision is to optimize all of these technology assets to provide enabling solutions for our customers –we are not just a supplier of a bag of parts.".

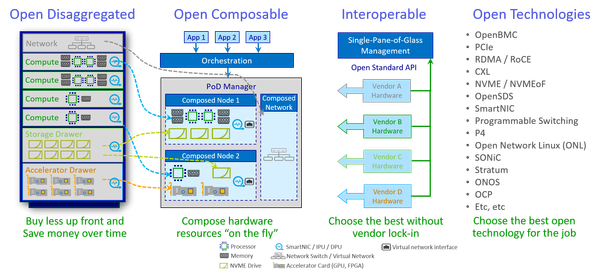

And then Hou goes on: "So let’s fast forward by five years. Ethernet is going to evolve from just end point connectivity and will enter the CPU from a SmartNIC, or whatever we might end up calling it, to offload some critical workload and to accelerate some of the workloads and to provide that performance enhancement for the network. This SmartNIC will integrate with CPUs, GPUs, FPGAs for compute and there may also be memory devices. We see that clear trend, and we are putting concerted effort in our development…. "

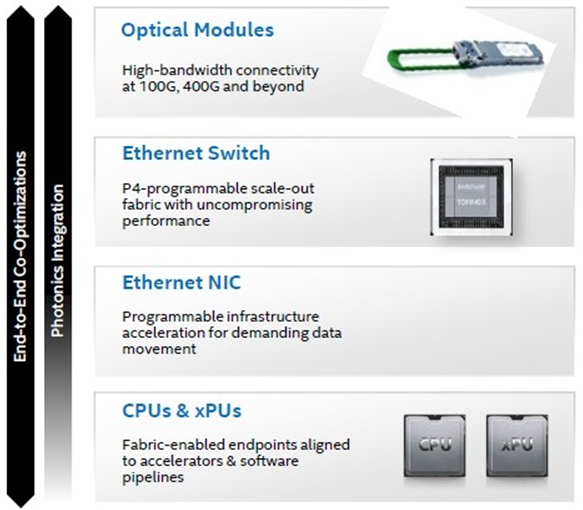

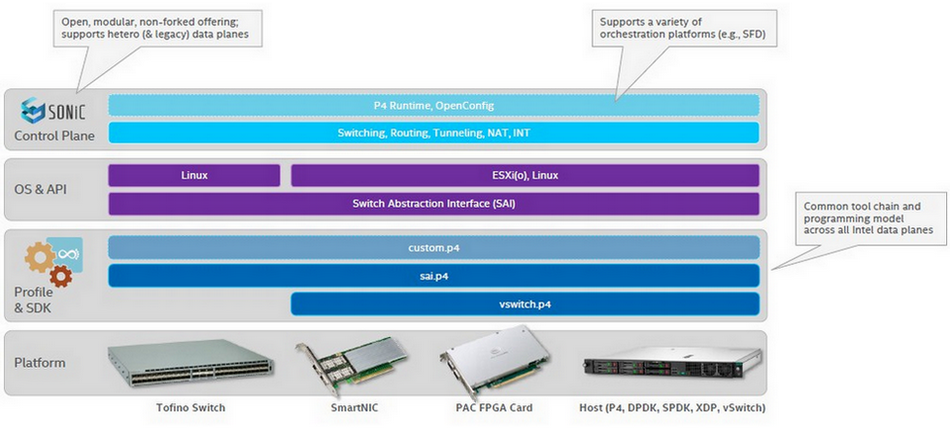

This vision statement maybe explains the, for most people, unexpected acquisition of Barefoot Networks Inc. as it brought Intel a new play in switching hardware (with the Tofino and Tofino2 switch chips) and maybe even more important, a extended grip in the total networking software ecosystem and not only the host networking communities they were previously reaching out to by developing DPDK and other networking libraries.

But what could P4 and programmability give Intel in the NIC space?

A couple of months ago Intel announced it “…will open source the Tofino architecture to ensure programmable packet processors are as open as CPUs.”.

In the weeks after Intel removed the NDA ban on publicising P4 code with Barefoot Tofino enhancements and the code related to driver calling.

Last week Intel went further, as stated in the connectivity division vision press release: "Today, we announced we are bringing together Intel Tofino switch silicon and Intel Stratix 10 FPGA to deliver scalable performance for demanding applications at the edge. The combined programmable switch and functionalities of an Intel FPGA offer comprehensive capabilities for packet processing that can be used by cloud service providers, communications service providers or at the network edge."

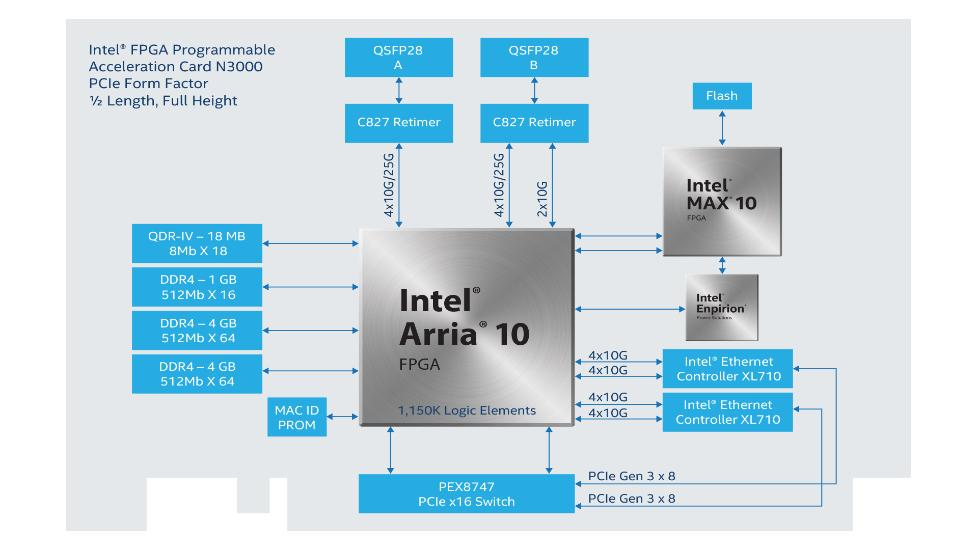

But is this all?? This are in itself nice moves but they won't stir up the NIC and networking environment a lot. Maybe we have to look in more detail to what happened with the PAC N3000 card in the last two years and to the information surrounding the 'SmartNIC' announcement made at the strategy communication session.

1,5 years ago Intel announced the 'Programmable Acceleration Card' PAC N3000. It consists of an Arria 10 FPGA bundled with two XL710 NIC chips as interface to the host CPU and the OS running on it. That was by the way one of the first results of an integrated board solution of another, at the end of 2015 by Intel acquired, company called Altera. ;-)

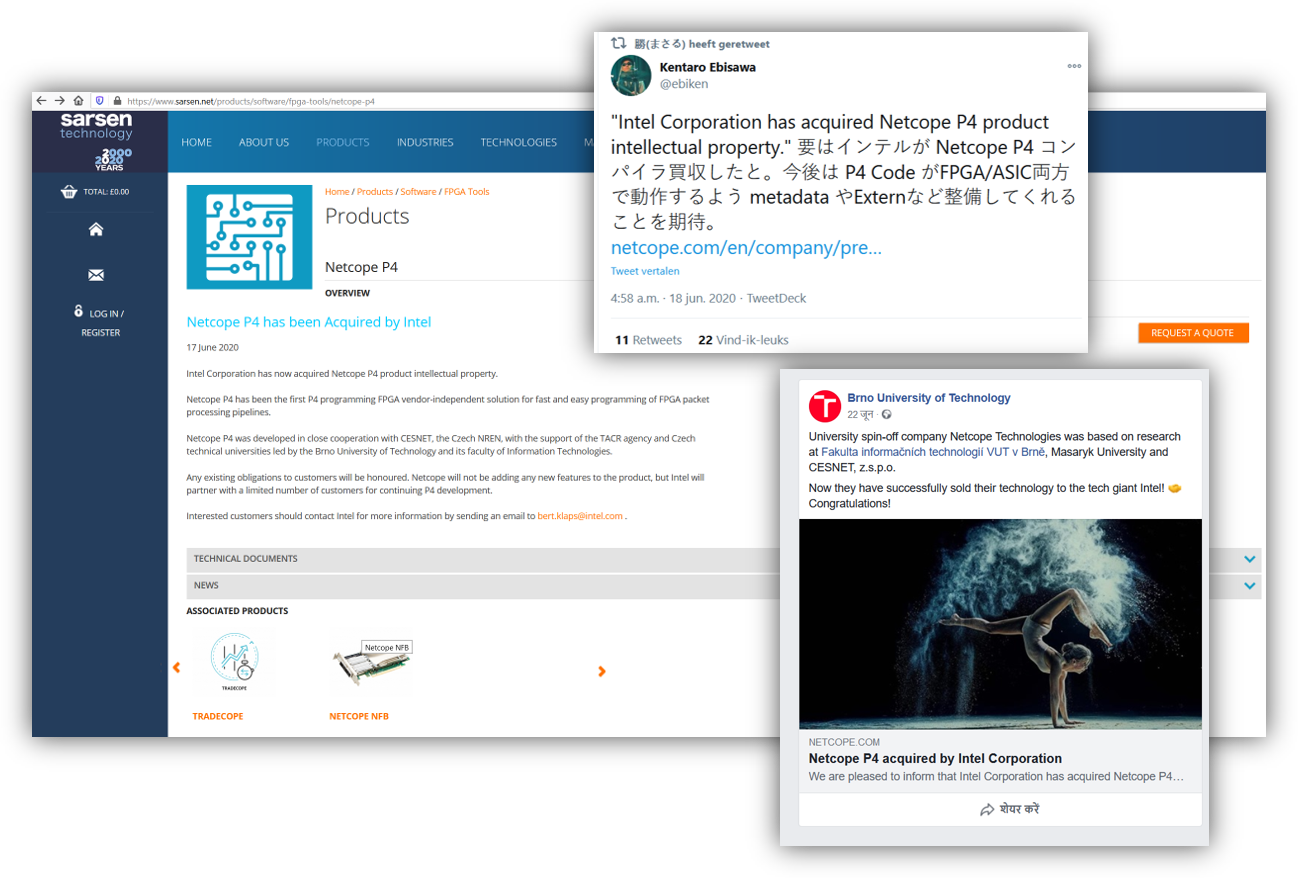

Intel mostly pushed the PAC N3000 as Programmable Acceleration Card for mobile 4/5G FlexRAN use. But a small company called Netcope saw another use case: it developed a service to compile P4 program code to a FPGA bitstream usable on the N3000 (and other FPGAs), creating, in a sense, a mini P4 programmable switch right in front of a server that could offload a lot of network handling from software to hardware.

Netcope P4 solution

The Netcope P4 solution is a framework that enables the programming of packet processing pipelines on FPGAs targets with the use of P4 language. The idea is to allow users to write P4 code for various FPGA-based SmartNICs. Such an approach does not require from the user any expert knowledge of how the given hardware is designed or what’s under the proverbial hood of this FPGA chip. Not knowing hardware description language (HDL) is also not a blocking point. What the user needs to do is upload the P4 code to Netcope’s P4 compilation platform, which contains the P4-to-HDL compiler. When the P4 code synthesis process is finished, the user can download the optimized firmware and load it into the given FPGA-based SmartNIC. That's neat eh!?

That's was what Intel was thinking too, so they acquired the P4 IP from Netcope in June 2020. There was a small press announcement from the sale by Netcope but that was removed again from the Internets very fast, probably Intel didn't want to wake up the competition (read Xilinx, Mellanox/Nvidia, Broadcom)…

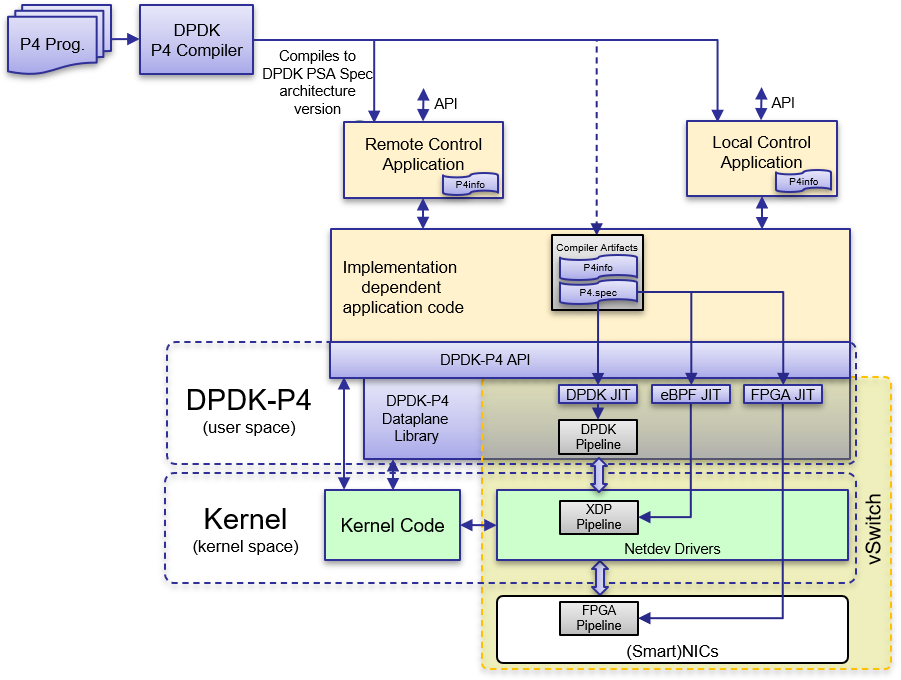

If you combine the IP from Netcope with the P4 compiler and pipeline knowledge of Barefoot and the in-house knowledge of how to program the FPGAs with specific offloading IP (like encryption, buffering and queueing etc) they could create a extended version of a Tofino2 PISA pipeline in FPGA code. The pipeline would configurable by a specification file created by a 'P4 to Intel P4 FPGA Pipeline' compiler and controlled by a DPDK user space module.

That could be the killer function the whole (P4) networking community is waiting for: end-to-end programmable P4 networking with the same accompanying compiler for switch hardware, network-to-host FPGA SmartNICs and software switching with P4-DPDK code. If only this was true….

The Intel vision execution until now…

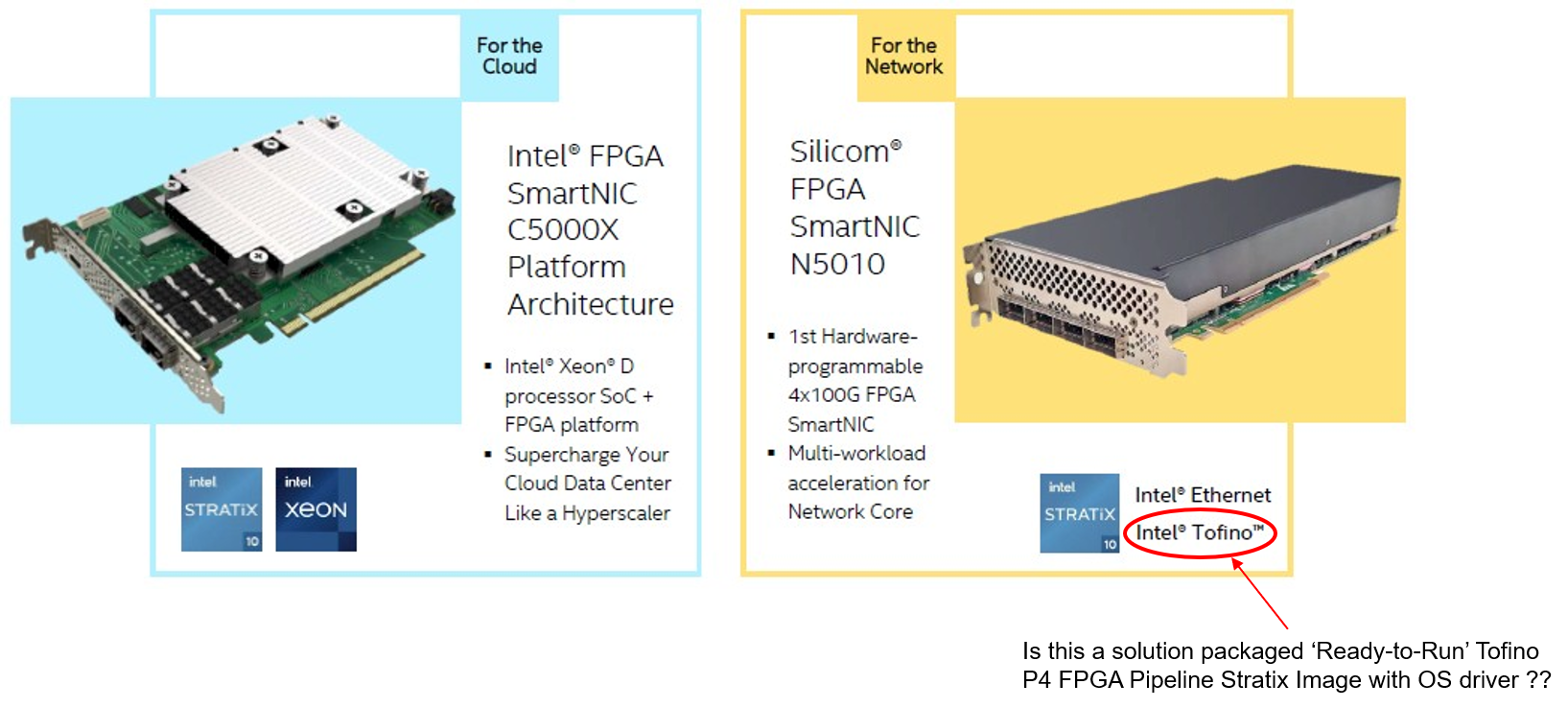

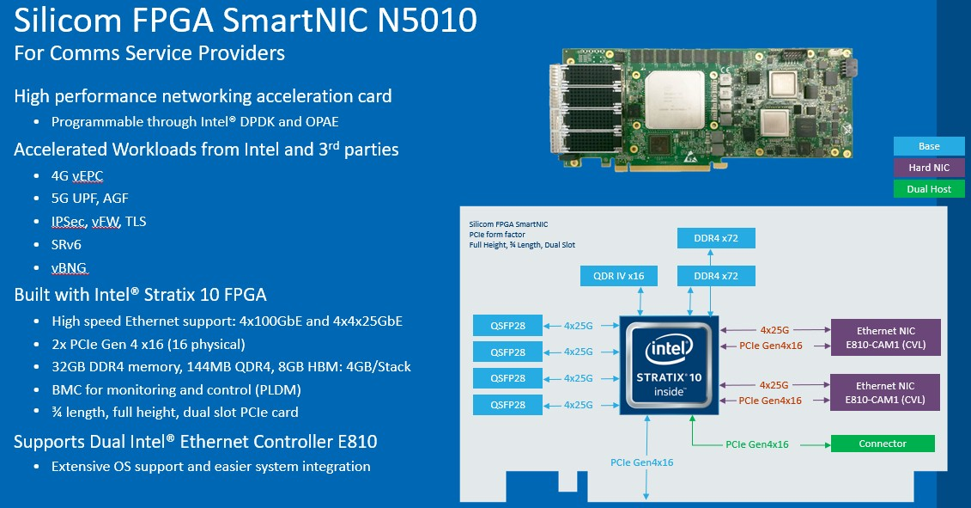

Last October Intel announced two, to host networking dedicated, SmartNICs platforms: the C5000X and the N5010. On its own this is just like any other SmartNIC announcement. The C5000X platform is different because an Xeon chip is embedded on the NIC instead of ARM cores and the N5010 is different because of… the 4x 100Gbit interfaces? Or is it something else like the Intel Tofino reference in the right hand corner of the next figure!

In my opinion this is the first release of hardware on which the end to end programmable networking vision of Intel could be created. They needed this SmartNIC line-up fast to get the NIC programmable software ecosystem started before others did and this where the missing hardware building blocks that had to be available.

The future…

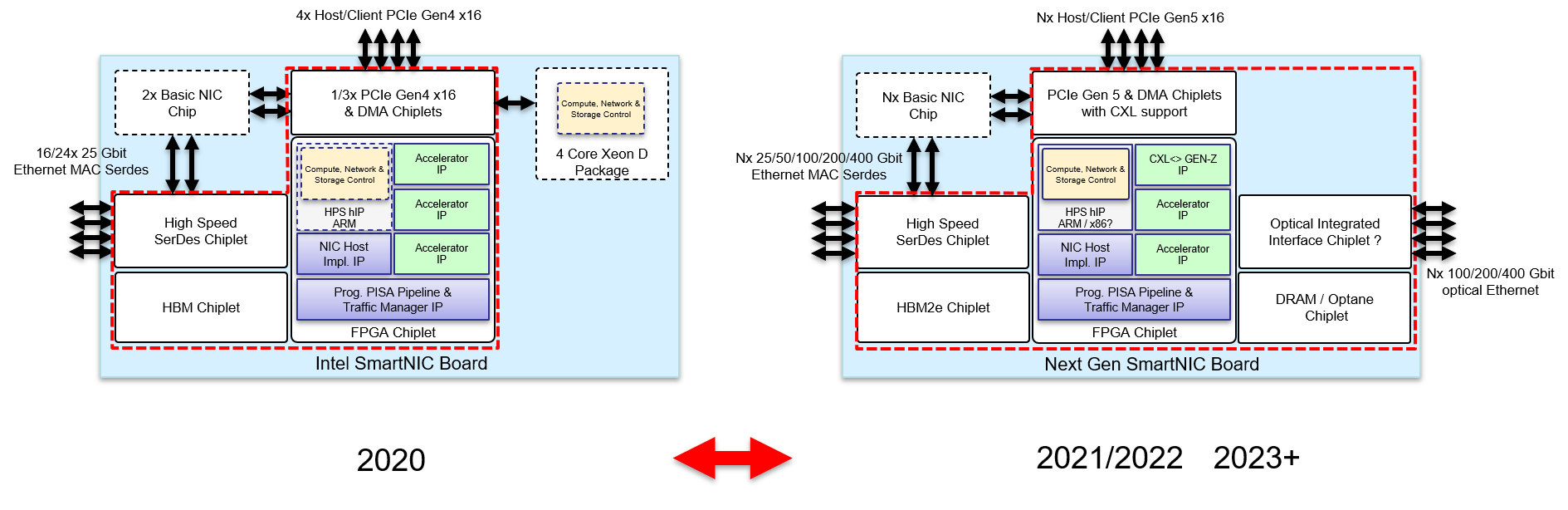

My vision is that later SmartNIC hardware versions will integrate foundational NIC chiplet, silicon photonics (in house!) and next generation PCIe 5 chiplet supporting CXL and GEN-Z with the at that moment available appropriate FPGA (read Agilex M series), using the chiplet technology created by Intel itself. To throw the gauntlet: I could even imagine a x86 chiplet with some x86 cores being integrated on even later versions of a SmartNIC package. ;-)

The reason for this high level of integration is lower used space and power/heath dissipation so that everything could be fitted on one OCP NICv3 interface card.

Summary

Intel communicated a comprehensive vision on the future of e2e networking/ (Smart)NICs and the role of Intel in it. They announced two new promising programmable SmartNICs, next to the available N3000 PAC, to expand their portfolio reach. But it is still unclear how OEMs, integrators and end customers could speed-up and expand their business with them, because an open integrated, easy to use comprehensive supporting software solution is still missing from their portfolio. Although as described a breakthrough on that front could not be far away….